**ONLINE COURSE : COVID-19 ZOOM VIDEO CLASSES**

SUBJECT : MICROPROCESSOR & MICROCONTROLLER BY

Dr. K. RASADURAI Department of Electronics and Communications Engineering KUPPAM ENGINEERING COLLEGE, Kuppam – 517425, Chittoor Dist., Andhra Pradesh

## CONTENT

- 1. I/O ports pull up/down resistors concepts

- 2. Interrupts and interrupt programming

- 3. Watchdog timer

- 4. System clocks

- 5. Low Power aspects of MSP430:

a. low power modes,

**b.** Active vs Standby current consumption

- 6. FRAM vs Flash for low power & reliability

- 7. Timer & Real Time Clock (RTC)

- 8. PWM control, timing generation and measurements

- 9. Analog interfacing and data acquisition:

- a. ADC and Comparator in MSP430,

- b. Data transfer using DMA.

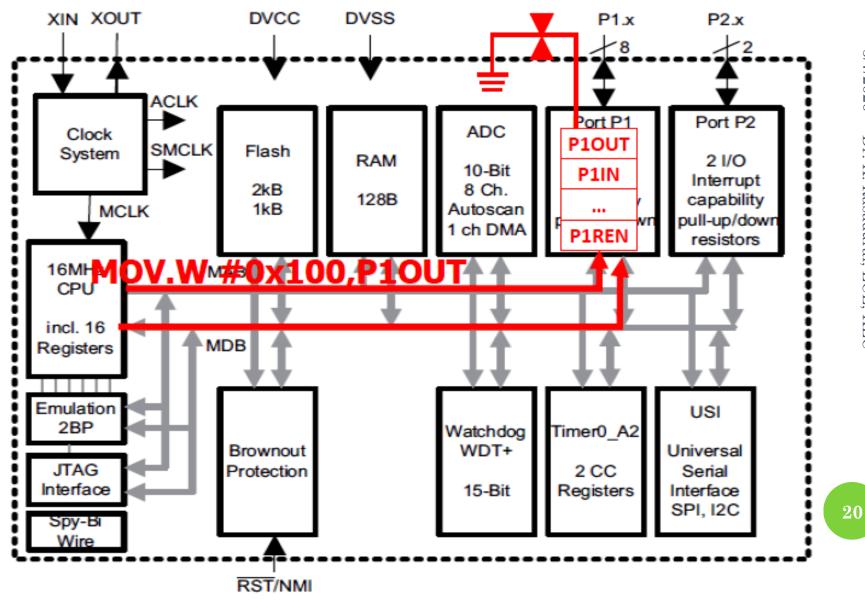

## **GPIO – REGISTERS OR DIGITAL I/O**

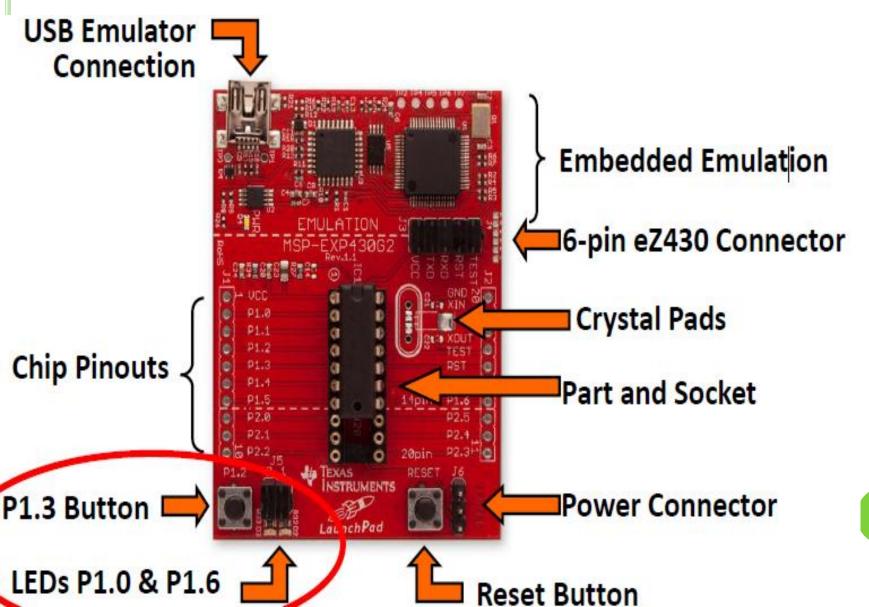

### MSP 430 - GENERAL PURPOSE IO LAUNCH PAD DEVELOPMENT BOARD

#### **1. GENERAL PURPOSE INPUT OUTPUT (GPIO)**

- one of the simplest integrated peripherals of the MSP430.

- General Purpose 8-bit Input Output (GPIO).

- The Input / Output (I/O) ports can be configured as interruptible or non-interruptible.

- Additionally, the port pins can be individually configured for general-purpose use, or

- as special function I/Os, such as USARTs, comparator signals and ADCs.

### **GENERAL PURPOSE IO**

MSP430 device, there can be up to ten 8-bit digital Input/Output (I/O) ports, named P1 to P10.

Typically, the MSP430 I/O ports P1 and P2 have interrupt capability.

Each interrupt on these I/O lines can be individually configured to provide an interrupt on a rising edge or falling edge of an input signal.

All I/O lines with interrupt capacity use a single interrupt vector.

The available digital I/O pins are:

-eZ430-F2013 MSP430 USB Stick: 10 pins - Port P1 (8 bits) and Port P2 (2 bits)

- eZ430-RF2500 MSP430 USB Stick: 32 pins - Ports P1 to P4 (8 bits)

- MSP430FG4618/F2013 Experimenter board: 80 pins – Ports P1 to P10 (8 bits). Ports P7/P8 and P9/P10 can be accessed as 16- bit values (words) as ports PA and PB respectively.

## MSP 430 GPIO

Each of these I/O ports has the following capacity:

-Independently programmable

-Combined input, output, and interrupt conditions;

- Edge-selectable interrupt inputs for all the 8 bits of ports P1 and P2

- Read/write access to port-control registers supported by all two or one-address instructions

- Each I/O has an individually programmable pullup / pulldown resistor (2xx family only).

Individually configured as special functions I/O, for example:

- USART Universal Synchronous/Asynchronous Receive/Transmit

- Comparative signals

- Analogue-to-Digital converter

- Amongst others...

# **GPIO – REGISTERS**

Independent of the I/O port type

- (non-interruptible: P3 and others) or

- interruptible (P1 and P2),

**1. Direction Registers (PxDIR)**

2. Input Registers (PxIN)

3. Output Registers (PxOUT)

4. Pull-up/Pull-down Resistor Enable Registers (PxREN)

5. Output Drive Strength Registers (PxDS)

6. Function Select Registers: (PxSEL) and (PxSEL2)

7. Interruptible ports (P1 and P2)

a. Interrupt Edge Select Registers (PxIES)

**b. Interrupt Flag Registers (PxIFG)**

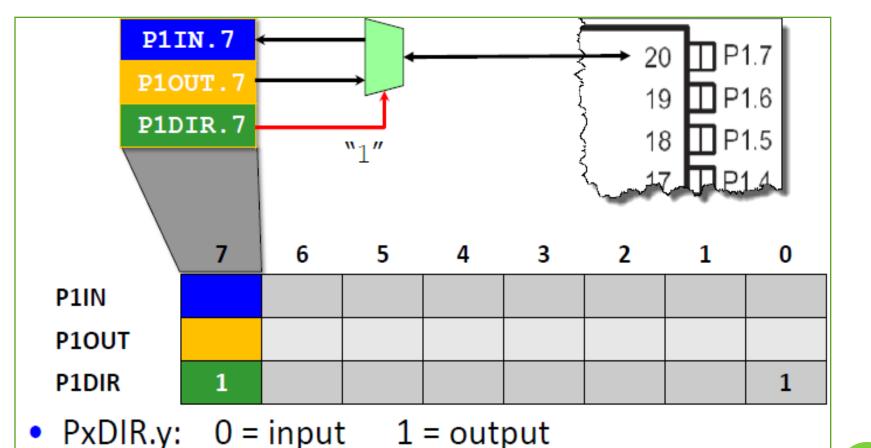

#### 1. Direction Registers (PxDIR)

- Read/write 8-bit registers;

- Selects the direction of the corresponding I/O pin, regardless of the selected function of the pin (general purpose I/O or as a special function I/O);

- Other module functions must be set as required by the other modules;

PxDIR configuration:

- Bit = 1: The port pin is set up as an output;

- Bit = 0: the port pin is set up as an input.

#### 2. Input Registers (PxIN)

- Each bit of these read-only registers reflects the input signal at the corresponding I/O pin (pin configured as general purpose I/O);

PxIN configuration:

- Bit = 1: The input is high;

- Bit = 0: The input is low;

- Tip: Avoid writing to these read-only registers because it will result in increased current consumption.

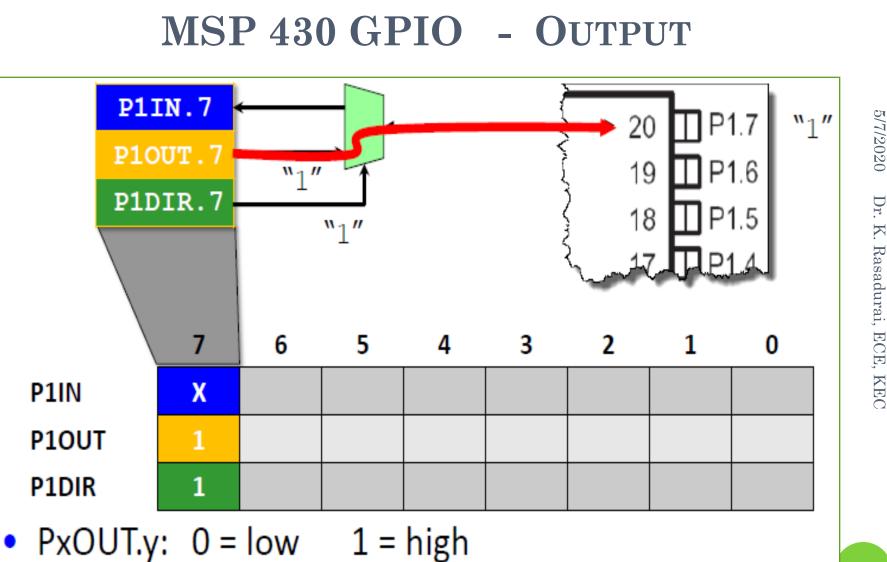

#### **3. Output Registers (PxOUT)**

- The output registers are read-write. Each bit of these registers reflects the value written to the corresponding output pin. PxOUT configuration:

- Bit = 1: The output is high

- Bit = 0: The output is low

- The 2xx family provides the additional feature that each I/O has a pullup/pulldown resistor that can be individually programmed. If the pin's ullup/pulldown resistor is enabled, the corresponding bit in the PxOUT register selects the pull-up or pull-down:

- Bit = 1: The pin is pulled up

Bit = 0: The pin is pulled down

#### 4. Pull-up/Pull-down Resistor Enable Registers (PxREN)

- Applies to the 2xx family only.

- Each bit of this register enables or disables the pullup / pulldown resistor of the corresponding I/O pin.

- PxREN configuration:

**Bit = 1: Pullup/pulldown resistor enabled**

□ Bit = 0: Pullup/pulldown resistor disabled

#### 5. Output Drive Strength Registers (PxDS)

- Each bit in each PxDS register selects either full drive or reduced drive strength. Default is reduced drive strength.

PxDS configuration:

- Bit = 0: Reduced drive strength

- Bit = 1: Full drive strength

#### 6. Function Select Registers: (PxSEL) and (PxSEL2)

- Some port pins are multiplexed with other peripheral module Functions.

- The bits: (PxSEL) and (PxSEL2 – 2xx family and some devices of the 47x(x) family), are used to select the pin function: I/O general-purpose port or peripheral module function.

PxSEL configuration:

□ Bit = 0: I/O function is selected for the pin;

□ Bit = 1: Peripheral module function is selected for the pin.

#### Function Select Registers: (PxSEL) and (PxSEL2).....

The 2xx family devices provide the PxSEL2 bit to configure additional features of the device. The PxSEL and PxSEL2 combination provides the following configuration of the 2xx devices:

□ Bit = 0: I/O function is selected for the pin;

$\Box$  Bit = 1: Peripheral module function is selected for the pin.

| PxSE<br>L | PxSEL<br>2 | Pin Function                                     |   |

|-----------|------------|--------------------------------------------------|---|

| 0         | 0          | Selects general-purpose I/O function             |   |

| 0         | 1          | Selects the primary peripheral module function   |   |

| 1         | 0          | Reserved (See device-specific data sheet)        | 1 |

| 1         | 1          | Selects the secondary peripheral module function |   |

#### 7. Interruptible ports (P1 and P2)

Each pin of ports P1 and P2 is able to generate an interrupt request (pin is interruptible) and is configured using the PxIFG, PxIE, and PxIES registers. The port makes use of all the same configuration registers as non-interruptible ports (as described above), but with three additional registers:

#### **Interrupt Enable (PxIE)**

□ Read-write register to enable interrupts on individual pins;

□ PxIE configuration:

$\Box$  Bit = 1: The interrupt is enabled;

$\Box$  Bit = 0: The interrupt is disabled.

□ Each PxIE bit enables the interrupt request associated with the

corresponding PxIFG interrupt flag;

□ Writing to PxOUT and/or PxDIR can result in setting PxIFG.

#### 7. Interruptible ports (P1 and P2)

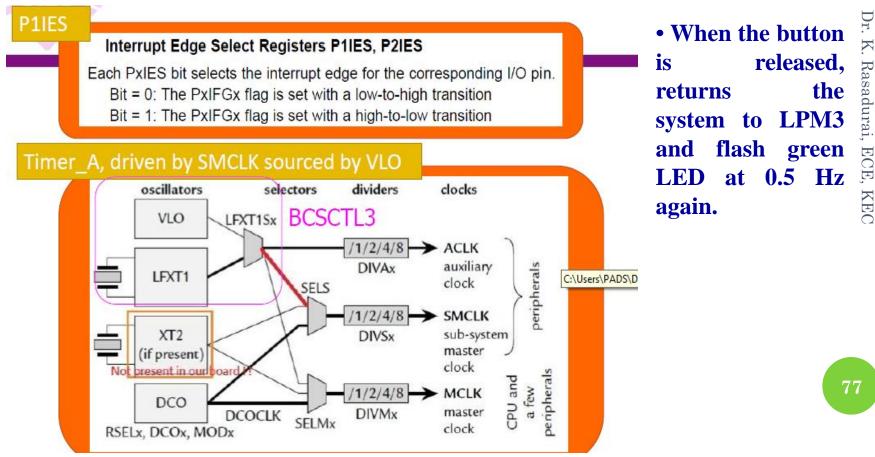

a. Interrupt Edge Select Registers (PxIES)

$\Box$  This read-write register selects the transition on which an interrupt occurs for the corresponding I/O pin

□ PxIES configuration:

\* Bit = 1: Interrupt flag is set on a high-to-low transition

\* Bit = 0: Interrupt flag is set on a low-to-high transition

#### **b.** Interrupt Flag Registers (PxIFG)

□ The bit of this read-write register is set automatically when the programmed signal transition (edge) occurs on the corresponding I/O pin, provided that the corresponding PxIE bit and the GIE bit are set

$\hfill\square$  Each PxIFG flag can be set by software, enabling an interrupt generated by software

$\Box$  Each PxIFG flag must be reset with software

- $\Box$  PxIFG configuration:

- \* Bit = 0: No interrupt is pending

- \* Bit = 1: An interrupt is pending

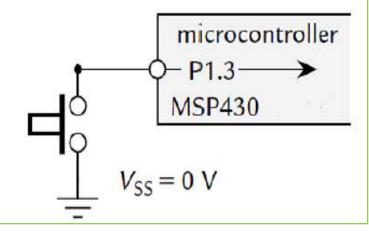

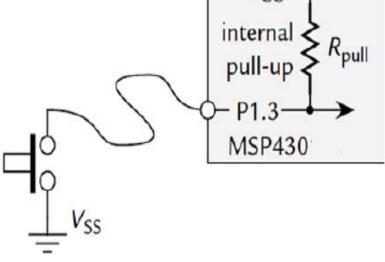

## **PROBLEM WITH INPUT USING A BUTTON**

- When the button is pressed down (closed), MSP430 will detect a 0 from the pin.

- When the button is up (open), what will MSP430 detect?

- Ans.: random value

- → Floating

16

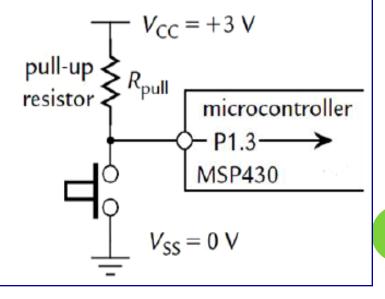

#### **TYPICAL WAY OF CONNECTING A BUTTON**

- The *pull-up resistor* R<sub>pull</sub> holds input at logic 1 (voltage V<sub>CC</sub>) while button is up and logic 0 or V<sub>SS</sub> when button is down → *active low*

- A wasted current flows through R<sub>pull</sub> to ground when button is down

- This is reduced by making  $R_{pull}$  large enough, typically 33  $k\Omega$

## **TYPICAL WAY OF CONNECTING A BUTTON**

- MSP430 offers internal pull-up/down

- PxREN register selects whether this resistor is used (1 to enable, 0 to disable)

- When enabled, the corresponding bit of PxOUT register selects whether the resistor pulls the input up to  $V_{cc}(1)$  or down to  $V_{ss}(0)$

```

#include <msp430g2553.h>

#define LED1 BIT0 //P1.0 to red LED

#define B1 BIT3 //P1.3 to button

void main(void) {

WDTCTL = WDTPW + WDTHOLD; //Stop watchdog timer

Plout \mid = LED1 + B1;

P1DIR = LED1; //Set pin with LED1 to output

PIREN = B1; //Set pin to use pull-up resistor

for(;;) { //Loop forever

if((P1IN & B1) ==0) { //Is button down or not

P1OUT &= ~LED1; // Turn LED1 off }

else{

P1OUT \mid = LED1; // Turn LED1 on }

```

```

#include <msp430.h>

void main(void) {

WDTCTL = WDTPW + WDTHOLD; // Stop watchdog

P1DIR |= 0x41; // set P1.0 & 6 to outputs

for(;;) {

volatile unsigned int i;

P1OUT ^= 0x41; // Toggle P1.0 & 6

i = 50000; // Delay

do (i--);

while (i != 0);

```

### GENERAL PURPOSE IO RECALL: MEMORY-MAPPED I/O

5/7/2020 Dr. K. Rasadurai, ECE, KEC

## GENERAL PURPOSE IO CONFIGURING THE I/O PORTS

| <b>Registers</b><br>(Mem Addr) | Functions                 | Descriptions                                                                                                                  |

|--------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| P1IN<br>(0x0020)               | Port 1 input              | This is a read-only register that reflects the<br>current state of the port's pins.                                           |

| P <i>1</i> OUT<br>(0x0021)     | Port 1 output             | The values written to this read/write register<br>are driven out to corresponding pins when<br>they are configured to output. |

| P1DIR<br>(0x0022)              | Port 1 data direction     | Bits written as 1 (0) configure the corresponding pins for output (input).                                                    |

| P1SEL<br>(0x0026)              | Port 1 function select    | Bits written as 1 (0) configure corresponding<br>pins for use by the specialized peripheral (for<br>general-purpose I/O).     |

| P1REN<br>(0x0027)              | Port 1 resistor<br>enable | Bits set in this register enable pull-up/down resistors on the corresponding I/O pins.                                        |

### MSP430 GPIO

TEST 1**O** GPIO = General 20 • Purpose Bit Vcc 19 P1.6 2 Input/Output P2.5 🔳 18 3 P1.5 • 8-bit I/O ports Vss 🔳 17 P1.4 4 P2.7 🔳 16 5 P1.3 Each pin is ٠ P2.6 15 P1.2 6 individually RST/NMI controllable 14 P2.0 P1.0 8 13 Controlled by ٠ P2.4 P2.1 12 9 memory-mapped P2.2 P2.3 11 registers P1.6 P1.5 P1.4 P1.2 P1.1 P1.0 P1.7 P1.3 I/O Port 1 Bit 7 Bit 6 Bit 4 Bit 2 Bit 1 Bit 5 Bit 3 Bit 0

22

5/7/2020

Dr. K. Rasadurai, ECE, KEC

## **PXDIR (PIN DIRECTION): INPUT OR OUTPUT**

Register example: P1DIR &= 0x81;

5/7/2020 Dr. K. Rasadurai, ECE, KEC

Register example: P1OUT &= 0x80;

Dr. K. Rasadurai, ECE, KEC

## **GPIO - SAMPLE CODE FOR INPUT**

```

#include <msp430g2231.h>

// Pins for LED and button on port 1

#define LED1 BIT0 //P1.0 to red LED

#define B1 BIT3 //P1.3 to button

void main(void) {

WDTCTL = WDTPW + WDTHOLD; //Stop watchdog timer

P1OUT |= LED1; //Preload LED1 on

P1DIR = LED1; //Set pin with LED1 to output

for(;;) { //Loop forever

if((P1IN & B1) ==0) { //Is button down or not

PIOUT &= ~LED1; // Turn IED1 off

P10UT is not initialized and

else{

PIOUT |= LED1; // T must be written before

configuring the pin for output.

```

| Offset | Acronym              | Register Name           | Туре       | Access | Reset     | Section        |

|--------|----------------------|-------------------------|------------|--------|-----------|----------------|

| 0Eh    | P1IV                 | Port 1 Interrupt Vector | Read only  | Word   | 0000h     | Section 1.4.1  |

| 0Eh    | P1IV_L               |                         | Read only  | Byte   | 00h       |                |

| 0Fh    | P1IV_H               |                         | Read only  | Byte   | 00h       |                |

| 1Eh    | P2IV                 | Port 2 Interrupt Vector | Read only  | Word   | 0000h     | Section 1.4.2  |

| 1Eh    | P2IV_L               |                         | Read only  | Byte   | 00h       |                |

| 1Fh    | P2IV_H               |                         | Read only  | Byte   | 00h       |                |

| 00h    | P1IN or<br>PAIN_L    | Port 1 Input            | Read only  | Byte   |           | Section 1.4.9  |

| 02h    | P1OUT or<br>PAOUT_L  | Port 1 Output           | Read/write | Byte   | undefined | Section 1.4.10 |

| 04h    | P1DIR or<br>PADIR_L  | Port 1 Direction        | Read/write | Byte   | 00h       | Section 1.4.11 |

| 06h    | P1REN or<br>PAREN_L  | Port 1 Resistor Enable  | Read/write | Byte   | 00h       | Section 1.4.12 |

| 08h    | P1DS or<br>PADS_L    | Port 1 Drive Strength   | Read/write | Byte   | 00h       | Section 1.4.13 |

| 046    | DICEL AF             | Dart 1 Dart Calant      | Pandhurita | Burke  | 005       | Contine 1.4.14 |

|        | PFREN L              |                         |            |        |           |                |

| 08h    | P11DS or<br>PFDS_L   | Port 11 Drive Strength  | Read/write | Byte   | 00h       | Section 1.4.1  |

| )Ah    | P11SEL or<br>PFSEL_L | Port 11 Port Select     | Read/write | Byte   | 00h       | Section 1.4.1  |

| )0h    | PAIN                 | Port A Input            | Read only  | Word   |           |                |

| 00h    | PAIN_L               |                         | Read only  | Byte   |           |                |

| 01h    | PAIN_H               |                         | Read only  | Byte   |           |                |

| )2h    | PAOUT                | Port A Output           | Read/write | Word   | undefined | 1              |

| )2h    | PAOUT L              |                         | Read/write | Byte   | undefined | I              |

| 03h    | PAOUT H              |                         | Read/write | -      | undefined |                |

| 04h    | PADIR                | Port A Direction        | Read/write |        |           | -              |

#### Table 1-2. Digital I/O Registers

$\mathbf{26}$

|   | OAh   | DECEL   |        |                |                   |      | Read/write | Dute | OOH |         |

|---|-------|---------|--------|----------------|-------------------|------|------------|------|-----|---------|

|   |       | PFSEL_L |        |                |                   |      |            | Byte |     | -       |

|   | OBh   | PFSEL_H |        |                |                   |      | Read/write | Byte | OOH | 1       |

|   | 00h   | PJIN    |        | Port J Input   |                   |      | Read only  | Word |     |         |

|   | 00h   | PJIN_L  |        |                |                   |      | Read only  | Byte |     |         |

|   | 01h   | PJIN_H  |        |                |                   |      | Read only  | Byte |     |         |

|   | 02h   | PJOUT   |        | Port J Output  | t                 |      | Read/write | Word | und | lefined |

|   | 02h   | PJOUT_L |        |                |                   |      | Read/write | Byte | und | lefined |

|   | 03h   | PJOUT_H |        |                |                   |      | Read/write | Byte | und | lefined |

|   | 04h   | PJDIR   |        | Port J Directi | on                |      | Read/write | Word | 000 | ODh     |

|   | 04h   | PJDIR_L |        |                |                   |      | Read/write | Byte | OOH | 1       |

|   | 05h   | PJDIR_H |        |                |                   |      | Read/write | Byte | OOH | 1       |

|   | 06h   | PJREN   |        | Port J Resist  | or Enable         |      | Read/write | Word | 000 | Oh      |

|   | 06h   | PJREN_L |        |                |                   |      | Read/write | Byte | OOH | 1       |

|   | 07h   | PJREN_H |        |                |                   |      | Read/write | Byte | OOH | 1       |

|   | 0.015 | , pipe  |        |                |                   |      | Deadhurite | Mand | 000 | ירי     |

|   |       | I       | nterru | pts vector     | <b>Register</b> 1 | P1IV |            |      |     |         |

| 1 | 5     | 14      | 13     | 12             | 11                | 10   | 9          | 8    |     |         |

|   |       |         |        | P1             | IV                |      |            |      |     | Jh      |

| r | 0     | rO      | r0     | D1             | r0                | гО   | 01         | rO   |     |         |

| 7 | 7     | 6       | 5      | 4              | 3                 | 2    | 1          | 0    |     |         |

|   |       |         |        | P1             | IV                |      |            |      |     |         |

| r | 0     | rO      | r0     | r-0            | r-0               | r-0  | r-0        | rO   |     |         |

|   |       |         |        |                |                   |      |            |      |     |         |

#### P1 IV Register Description

| Bit  | Field | Туре | Reset | Description                                                                                         |   |

|------|-------|------|-------|-----------------------------------------------------------------------------------------------------|---|

| 15-0 | P1IV  | R    | Oh    | Port 1 interrupt vector value                                                                       | 1 |

| 1    |       |      |       | 00h = No interrupt pending                                                                          |   |

|      |       |      |       | 02h = Interrupt Source: Port 1.0 interrupt; Interrupt Flag: P1IFG.0; Interrupt<br>Priority: Highest |   |

| 1    |       |      |       | 04h = Interrupt Source: Port 1.1 interrupt; Interrupt Flag: P1IFG.1                                 |   |

|      |       |      |       | 06h = Interrupt Source: Port 1.2 interrupt; Interrupt Flag: P1IFG.2                                 |   |

|      |       |      |       | 08h = Interrupt Source: Port 1.3 interrupt; Interrupt Flag: P1IFG.3                                 |   |

|      |       |      |       | 0Ah = Interrupt Source: Port 1.4 interrupt; Interrupt Flag: P1IFG.4                                 |   |

|      |       |      |       | 0Ch = Interrupt Source: Port 1.5 interrupt; Interrupt Flag: P1IFG.5                                 |   |

|      |       |      |       | 0Eh = Interrupt Source: Port 1.6 interrupt; Interrupt Flag: P1IFG.6                                 |   |

|      |       |      |       | 10h = Interrupt Source: Port 1.7 interrupt; Interrupt Flag: P1IFG.7; Interrupt<br>Priority: Lowest  |   |

|    |    | Inter | rupts vecto | or Registe | r P2IV |     |    |

|----|----|-------|-------------|------------|--------|-----|----|

| 15 | 14 | 13    | 12          | 11         | 10     | 9   | 8  |

|    |    |       |             |            |        |     |    |

| rO | rO | rO    | rO          | гО         | rO     | rO  | rO |

| 7  | 6  | 5     | 4           | 3          | 2      | 1   | 0  |

|    |    |       |             |            |        |     |    |

| rO | rO | 01    | r-0         | r-0        | r-0    | r-0 | rO |

#### **P2 IV Register Description**

| Bit  | Field | Туре | Reset | Description                                                                                         |

|------|-------|------|-------|-----------------------------------------------------------------------------------------------------|

| 15-0 | P2IV  | R    | Oh    | Port 2 interrupt vector value                                                                       |

|      |       |      |       | 00h = No interrupt pending                                                                          |

|      |       |      |       | 02h = Interrupt Source: Port 2.0 interrupt; Interrupt Flag: P2IFG.0; Interrupt<br>Priority: Highest |

|      |       |      |       | 04h = Interrupt Source: Port 2.1 interrupt; Interrupt Flag: P2IFG.1                                 |

|      |       |      |       | 06h = Interrupt Source: Port 2.2 interrupt; Interrupt Flag: P2IFG.2                                 |

|      |       |      |       | 08h = Interrupt Source: Port 2.3 interrupt; Interrupt Flag: P2IFG.3                                 |

|      |       |      |       | 0Ah = Interrupt Source: Port 2.4 interrupt; Interrupt Flag: P2IFG.4                                 |

|      |       |      |       | 0Ch = Interrupt Source: Port 2.5 interrupt; Interrupt Flag: P2IFG.5                                 |

|      |       |      |       | 0Eh = Interrupt Source: Port 2.6 interrupt; Interrupt Flag: P2IFG.6                                 |

|      |       |      |       | 10h = Interrupt Source: Port 2.7 interrupt; Interrupt Flag: P2IFG.7; Interrupt<br>Priority: Lowest  |

5/7/2020 Dr. K. Rasadurai, ECE, KEC

| P1 IES | Register | P1IES Register |     |    |    |     |    |  |  |

|--------|----------|----------------|-----|----|----|-----|----|--|--|

| 7      | 6        | 5 4 3 2 1 0    |     |    |    |     |    |  |  |

|        |          |                | P1I | ES |    |     |    |  |  |

| rw     | rw       | rw             | rw  | rw | rw | rw. | rw |  |  |

#### P1IES Register Description

| BIt | Field | Туре | Reset | Description                                                                                                                                    |  |  |

|-----|-------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7-0 | PIIES | RW   |       | Port 1 Interrupt edge select<br>0b = P1IFG flag is set with a low-to-high transition.<br>1b = P1IFG flag is set with a high-to-low transition. |  |  |

#### P1 IE Register

|      | . P1IE Register |      |      |      |      |      |      |  |  |  |

|------|-----------------|------|------|------|------|------|------|--|--|--|

| 7    | 6               | 5    | 4    | 3    | 2    | 1    | 0    |  |  |  |

|      | PIIE            |      |      |      |      |      |      |  |  |  |

| rw-0 | rw-0            | rw-0 | rw-0 | rw-0 | rw-0 | rw-0 | rw-0 |  |  |  |

#### P1IE Register Description

| BIt | Field | Туре | Reset | Description                                                                                                        |

|-----|-------|------|-------|--------------------------------------------------------------------------------------------------------------------|

| 7-0 | PIIE  | RW   |       | Port 1 Interrupt enable<br>Ob - Corresponding port Interrupt disabled<br>1b - Corresponding port Interrupt enabled |

#### P1 IFG Register

|      | _ P1IFG Register |      |      |      |      |      |      |  |  |  |

|------|------------------|------|------|------|------|------|------|--|--|--|

| 7    | 6                | 5    | 4    | 3    | 2    | 1    | 0    |  |  |  |

|      |                  |      | P1   | FG   |      |      |      |  |  |  |

| rw-0 | rw-0             | rw-0 | rw-0 | rw-0 | rw-0 | rw-0 | rw-0 |  |  |  |

#### P1IFG Register Description

| BIt | Field | Туре | Reset | Description                                                                        |

|-----|-------|------|-------|------------------------------------------------------------------------------------|

| 7-0 | P1IFG | RW   |       | Port 1 Interrupt flag<br>Ob = No Interrupt is pending<br>1b = Interrupt is pending |

## **INTERRUPTS**

#### **INTERRUPTS ARE COMMONLY USED FOR A RANGE OF APPLICATIONS:**

- Urgent tasks that must be executed promptly at higher priority than 0 the main code.

- However, it is even faster to execute a task directly by hardware if this 0

- is possible. Infrequent tasks, such as handling slow input from humans. This saves the overhead of regular polling. Waking the CPU from sleep. (a low-power mode and can be awakened only by on intervent) 0

- 0 only by an interrupt).

- Calls to an operating system. A substitute is for software to set an 0 unused interrupt flag for one of the peripherals, such as port P1 or P2.

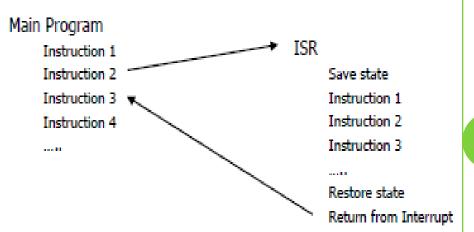

#### **INTERRUPTS - HANDLED**

- The code that was interrupted can be resumed without error. (the values in the CPU registers must be restored).

- The hardware can take two extreme approaches to this:

- Copies of all the registers are saved on the stack automatically as part of the process for entering an interrupt.

- The opposite approach is for the hardware to save only the absolute minimum, which is the return address in the PC as in a subroutine.

- This is much faster but it is up to the user to save and restore values of the critical registers, notably the status register.

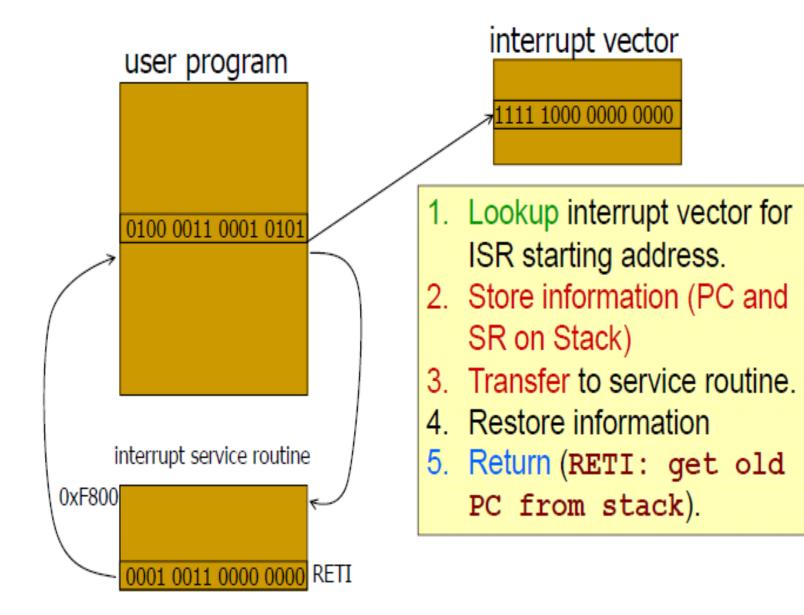

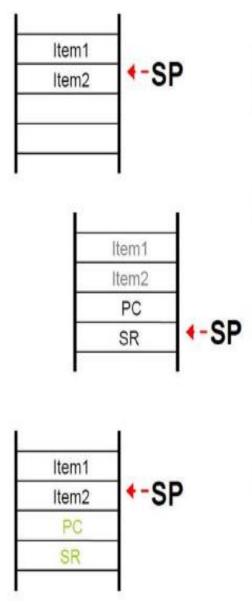

#### WHAT HAPPENS WHEN AN INTERRUPT IS REQUESTED?

Hardware then performs the following steps to launch the ISR:

- 1. Any currently executing instruction is completed if the CPU was active when the interrupt was requested. MCLK is started if the CPU was off.

- 2. The PC, which points to the next instruction, is pushed onto the stack.

- 3. The SR is pushed onto the stack.

- 4. The interrupt with the highest priority is selected if multiple interrupts are waiting for service.

- 5. The interrupt request flag is cleared automatically for vectors that have a single source. Flags remain set for servicing by software if the vector has multiple sources, which applies to the example of TAIFG.

- 6. The SR is cleared, which has two effects. First, further maskable interrupts are disabled because the GIE bit is cleared; nonmaskable interrupts remain active. Second, it terminates any low-power mode

- 7. The interrupt vector is loaded into the PC and the CPU starts to execute the interrupt service routine at that address.

- This sequence takes six clock cycles in the MSP430 before the ISR commences. The stack at this point is shown in Figure 6.5. The position of SR on the stack is important if the low-power mode of operation needs to be changed.

### **MSP430 - INTERRUPTS**

- Reaction to something in I/O (human, comm link)

- Usually asynchronous to processor activities

- "interrupt handler" or "interrupt service routine" (ISR) invoked to take care of condition causing interrupt

- Change value of internal variable (count)

- Read a data value (sensor, receive)

- Write a data value (actuator, send)

## MSP430 - INTERRUPTS

- Interrupts preempt normal code execution

- Interrupt code runs in the foreground

- Normal (e.g. main()) code runs in the background

- Interrupts can be enabled and disabled

- Globally

- Individually on a per-peripheral basis

- Non-Maskable Interrupt (NMI)

- The occurrence of each interrupt is unpredictable

- When an interrupt occurs

- Where an interrupt occurs

- Interrupts are associated with a variety of on-chip and off-chip peripherals.

- Timers, Watchdog, D/A, Accelerometer

- NMI, change-on-pin (Switch)

## **MSP430** - INTERRUPTS

Interrupts commonly used for

- Urgent tasks w/higher priority than main code

- Infrequent tasks to save polling overhead

- Waking the CPU from sleep

- □ Call to an operating system (software interrupt).

# Event-driven programming

- The flow of the program is determined by events—i.e., sensor outputs or user actions (mouse clicks, key presses) or messages from other programs or threads.

- The application has a main loop with event detection and event handlers.

# **INTERRUPT FLAGS**

- Each interrupt has a flag that is raised (set) when the interrupt occurs.

- Each interrupt flag has a corresponding enable bit – setting this bit allows a hardware module to request an interrupt.

- Most interrupts are *maskable*, which means they can only interrupt if

- 1) enabled and

- the general interrupt enable (GIE) bit is set in the status register (SR).

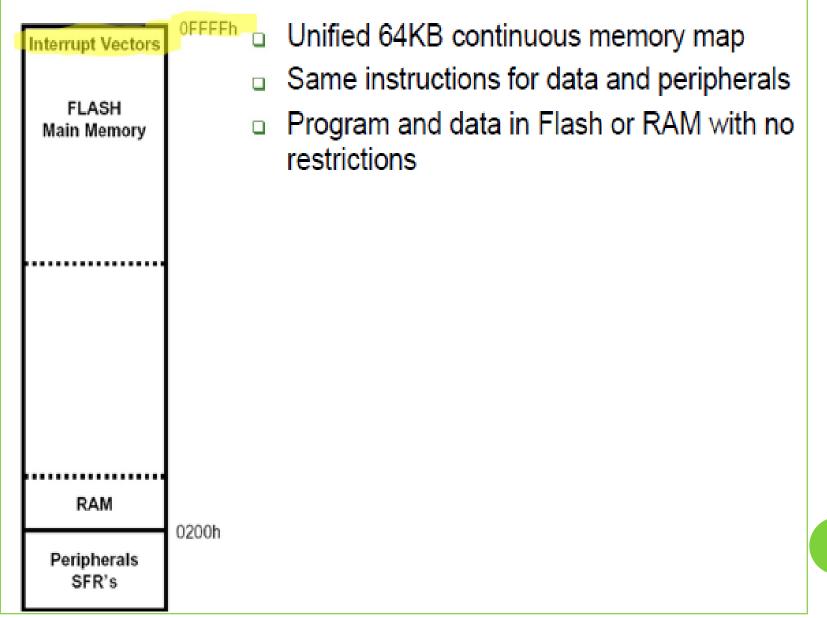

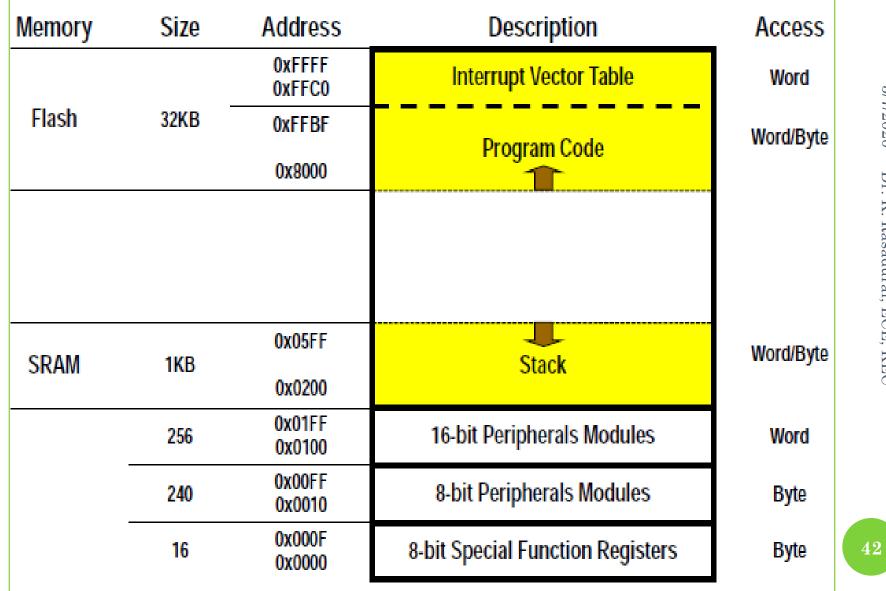

#### **INTERRUPT VECTORS**

- The CPU must know where to fetch the next instruction following an interrupt.

- The address of an ISR is defined in an interrupt vector.

- The MSP430 uses vectored interrupts where each ISR has its own vector stored in a vector table located at the end of program memory.

- Note: The vector table is at a fixed location (defined by the processor data sheet), but the ISRs can be located anywhere in memory.

#### **INTERRUPT MEMORY**

# SERVING INTERRUPT REQUEST

## **MSP430**x2xx INTERRUPT VECTORS

| Table 7. Interrupt Sources                                                                             |                                                            |                                                      | Higher address -> higher |                 | er priorit |

|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------|--------------------------|-----------------|------------|

| INTERRUPT SOURCE                                                                                       | INTERRUPT FLAG                                             | SYSTEM<br>INTERRUPT                                  | WORD ADDRESS             | PRIORITY        |            |

| Power-up<br>External reset<br>Watchdog Timer+<br>Flash key violation<br>PC out-of-range <sup>(1)</sup> | PORIFG<br>RSTIFG<br>WDTIFG<br>KEYV<br>See (2)              | Reset                                                | OFFFEh                   | 31, highest     | 5/7/2020   |

| NMI<br>Oscillator fault<br>Flash memory access violation                                               | NMIIFG<br>OFIFG<br>ACCVIFG <sup>(2)(3)</sup>               | (non)-maskable,<br>(non)-maskable,<br>(non)-maskable | OFFFCh                   | 30              | Dr. K.     |

|                                                                                                        |                                                            |                                                      | OFFFAh                   | 29              |            |

|                                                                                                        |                                                            |                                                      | OFFF8h                   | 28              | Rasadurai, |

| Comparator_A+ (MSP430F20x1)                                                                            | CAIFG <sup>(#)</sup>                                       | maskable                                             | OFFFöh                   | 27              | dur        |

| Watchdog Timer+                                                                                        | WDTIFG                                                     | maskable                                             | OFFF4h                   | 28              |            |

| Timer_A2                                                                                               | TACCR0 CCIFG <sup>(4)</sup>                                | maskable                                             | OFFF2h                   | 25              | ECE,       |

| Timer_A2                                                                                               | TACCR1 CCIFG.TAIFG <sup>(2)(4)</sup>                       | maskable                                             | OFFFOh                   | 24              | Ĕ,         |

|                                                                                                        |                                                            |                                                      | OFFEEh                   | 23              | KEC        |

|                                                                                                        |                                                            |                                                      | OFFECh                   | 22              | Ω          |

| ADC10 (MSP430F20x2)                                                                                    | ADC10(FG <sup>(4)</sup>                                    | maskable                                             | OFFEAh                   | 21              |            |

| SD16_A (MSP430F20x3)                                                                                   | SD16CCTL0 SD16OVIFG<br>SD16CCTL0 SD16IFG <sup>(2)(4)</sup> | maskable                                             |                          |                 |            |

| USI<br>(MSP430F20x2, MSP430F20x3)                                                                      | USIIFG, USISTTIFG <sup>(2)(4)</sup>                        | maskable                                             | OFFER                    | 20              |            |

| I/O Port P2 (two flags)                                                                                | P2IFG.6 to P2IFG.7 <sup>(25)4)</sup>                       | maskable                                             | OFFECh                   | 19              |            |

| I/O Port P1 (eight flags)                                                                              | P1IFG.0 to P1IFG.7 <sup>(2)(4)</sup>                       | maskable                                             | OFFE4h                   | 18              | 41         |

|                                                                                                        |                                                            |                                                      | OFFE2h                   | 17              |            |

|                                                                                                        |                                                            |                                                      | OFFEOh                   | 16              |            |

| See (5)                                                                                                |                                                            |                                                      | OFFDEh to OFFCOh         | 15 to 0, lowest |            |

# **MSP430F2274 Address Space**

5/7/2020

Dr. K. Rasadurai, ECE, KEC

# **PROCESSING AN INTERRUPT.....**

- 1) Current instruction completed

- MCLK started if CPU was off

- 3) Processor pushes program counter on stack

- 4) Processor pushes status register on stack

- 5) Interrupt w/highest priority is selected

- Interrupt request flag cleared if single sourced

- 7) Status register is cleared

- Disables further maskable interrupts (GIE cleared)

- Terminates low-power mode

- Processor fetches interrupt vector and stores it in the program counter

- 9) User ISR must do the rest!

#### **INTERRUPT STACK**

# Prior to Interrupt Service Routine (=ISR)

# ISR hardware - automatically

- Program Counter (= PC) pushed

- Status Register (= SR) pushed

- Interrupt vector moved to PC

- GIE, CPUOFF, OSCOFF and SCG1 cleared

- IFG flag cleared on single source flags

# reti - automatically

- SR popped original

- PC popped

# **INTERRUPT SERVICE ROUTINES**

- Look superficially like a subroutine.

- However, unlike subroutines

- ISR's can execute at unpredictable times.

- Must carry out action and thoroughly clean up.

- Must be concerned with shared variables.

- Must return using *reti* rather than *ret*.

- ISR must handle interrupt in such a way that the interrupted code can be resumed without error

- Copies of all registers used in the ISR must be saved (preferably on the stack)

### **INTERRUPT SERVICE ROUTINES**

# Well-written ISRs:

- Should be short and fast

- Should affect the rest of the system as little as possible

- Require a balance between doing very little thereby leaving the background code with lots of processing – and doing a lot and leaving the background code with nothing to do

- Applications that use interrupts should:

- Disable interrupts as little as possible

- Respond to interrupts as quickly as possible

#### **INTERRUPT SERVICE ROUTINES**

- Interrupt-related runtime problems can be exceptionally hard to debug

- Common interrupt-related errors include:

- □ Failing to protect global variables

- □ Forgetting to actually include the ISR no linker error!

- Not testing or validating thoroughly

- Stack overflow

- Running out of CPU horsepower

- Interrupting critical code

- □ Trying to outsmart the compiler

# **RETURNING FROM ISR**

- MSP430 requires 6 clock cycles before the ISR begins executing

- The time between the interrupt request and the start of the ISR is called *latency (plus time to complete the current instruction, 6 cycles, the worst case)*

- An ISR always finishes with the return from interrupt instruction (*reti*) requiring 5 cycles

- The SR is popped from the stack

- Re-enables maskable interrupts

- Restores previous low-power mode of operation

- The PC is popped from the stack

- Note: if waking up the processor with an ISR, the new power mode must be set in the stack saved SR

# **RETURN FROM INTERRUPT**

#### Single operand instructions:

|   | Mnemonic        |     | Operation                          | Description                    |

|---|-----------------|-----|------------------------------------|--------------------------------|

|   | push (.B or .W) | src | SP-2→SP, src→@SP                   | Push byte/word source on stack |

|   | CALL            | dst | SP-2→SP, PC+2→@SP<br>dst→PC        | Subroutine call to destination |

| ♦ | RETI            |     | TOS→SR, SP+2→SP<br>TOS→PC, SP+2→SP | Return from interrupt          |

#### Emulated instructions:

| Mnemonic        | Operation                       | Emulation                 | Description                             |

|-----------------|---------------------------------|---------------------------|-----------------------------------------|

| RET             | @SP→PC<br>SP+2→SP               | MOV @SP+,PC               | Return from subroutine                  |

| POP(.Bor.W) dst | @SP→temp<br>SP+2→SP<br>temp→dst | MOV(.B or .W)<br>@SP+,dst | Pop byte/word from stack to destination |

## SUMMARY

- By coding efficiently you can run multiple peripherals at high speeds on the MSP430

- Polling is to be avoided use interrupts to deal with each peripheral only when attention is required

- Allocate processes to peripherals based on existing (fixed) interrupt priorities - certain peripherals can tolerate substantial latency

- Use GIE when it's shown to be most efficient and the application can tolerate it – otherwise, control individual IE bits to minimize system interrupt latency.

- An interrupt-based approach eases the handling of asynchronous events

# **P1** AND **P2** INTERRUPTS

- Only transitions (low to hi or hi to low) cause interrupts

- P1IFG & P2IFG (Port 1 & 2 Interrupt FlaG registers)

- Bit 0: no interrupt pending

- Bit 1: interrupt pending

- P1IES & P2IES (Port 1 & 2 Interrupt Edge Select reg)

- Bit 0: PxIFG is set on low to high transition

- Bit 1: PxIFG is set on high to low transition

- P1IE & P2IE (Port 1 & 2 Interrupt Enable reg)

- Bit 0: interrupt disabled

- Bit 1: interrupt enabled

$\mathbf{51}$

# 5/7/2020 Dr. K. Rasadurai, ECE, KEC

# Example P1 interrupt msp430x20x3\_P1\_02.c

```

#include <msp430x20x3.h>

void main(void)

```

```

WDTCTL = WDTPW + WDTHOLD; // Stop watchdog timer

P1DIR \mid = 0 \times 01;

P1IE |= 0 \times 10;

Plies |= 0 \times 10;

P1IFG \&= \sim 0 \times 10;

```

```

// Set P1.0 to output direction

// P1.4 interrupt enabled

// P1.4 Hi/lo edge

// P1.4 IFG cleared

```

```

BIS SR(LPM4 bits + GIE); // Enter LPM4 w/interrupt

// Port 1 interrupt service routine

#pragma vector=PORT1 VECTOR

interrupt void Port 1 (void)

P1OUT ^{=} 0x01;

// P1.0 = toggle

// P1.4 IFG cleared

P1IFG \&= \sim 0 \times 10;

```

```

Ex: Timer interrupt: msp430x20x3_ta_03.c

#include <msp430x20x3.h>

void main(void)

// Stop WDT

WDTCTL = WDTPW + WDTHOLD;

P1DIR \mid = 0 \times 01;

// P1.0 output

TACTL = TASSEL 2 + MC 2 + TAIE;

// SMCLK, contmode, interrupt

BIS SR(LPM0 bits + GIE);

// Enter LPM0 w/ interrupt

// Timer A3 Interrupt Vector (TAIV) handler

#pragma vector=TIMERA1 VECTOR

interrupt void Timer A(void)

switch( TAIV )

// CCR1 not used

case 2: break;

// CCR2 not used

case 4: break;

case 10: P1OUT ^= 0x01;

// overflow

break;

```

5/7/2020 Dr. K. Rasadurai, ECE, KEC

**5**<u>3</u>

```

Msp430x20x3_ta_06.c (modified, part 1)

#include <msp430x20x3.h>

void main (void)

{

WDTCTL = WDTPW + WDTHOLD; // Stop WDT

// P1.0 output

P1DIR \mid = 0 \times 01;

CCTL1 = CCIE;

// CCR1 interrupt enabled

CCR1 = 0 \times A000;

TACTL = TASSEL 2 + MC 2; // SMCLK, Contmode

BIS SR(LPMO bits + GIE);// Enter LPMO w/ int.

}

```

Servicing a timer interrupt; toggling pin in ISR

$\mathbf{54}$

```

Msp430x20x3_ta_06.c (modified, part 2)

// Timer A3 Interrupt Vector (TAIV) handler

#pragma vector=TIMERA1 VECTOR

interrupt void Timer A(void)

switch( TAIV )

// CCR1

case 2:

Plout ^= 0x01; // Toggle Pl.0

CCR1 += 0xA000; // Add Offset to CCR1 == 0xA000

ł

break;

case 4: break; // CCR2 not used

case 10: break; // overflow not used

```

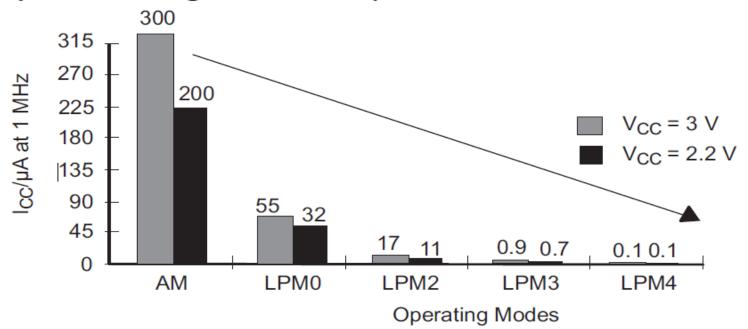

# LOW POWER MODES :

#### Energy and Power Énergy: ability to do work $\langle \mathbf{x} \rangle$ , OW POWER MODI - Most important in battery-powered systems Power: energy per unit time Important even in wall-plug systems---power becomes heat Power draw increases with ... – Vcc Clock speed Temperature gate gate drain drain source

Switching consumes power  $\rightarrow$  dynamic power

- Switching slower, consume less power

- Smaller sizes reduce power to operate

#### Leakage $\rightarrow$ static power

#### **Low-Power Optimization**

#### Why low power?

- Portable and mobile devices are getting popular, which have limited power sources, e.g., battery

- Energy conservation for our planet

- Power generates heat  $\rightarrow$  low carbon

- Power optimization becomes a new dimension in system design, besides performance and cost

Put the system in low-power modes and/or use lowpower modules as much as possible

#### How?

- Provide clocks of diff. frequencies

<del>Frequency scaling</del>

- Lower supplied voltage  $\rightarrow$  voltage scaling

- Turn off clocks when no work to do  $\rightarrow$  clock gating

- Use interrupts to wake up the CPU, return to sleep when done (another reason to use interrupts)

- Switched on peripherals only when needed

- Use low-power integrated peripheral modules in place of software, e.g., low-power DSP

- Clock gating for synchronous sequential logic:

- Disable the clock so that flip-flops will hold their states forever and the whole circuit will not switch

- $\rightarrow$  no dynamic power consumed

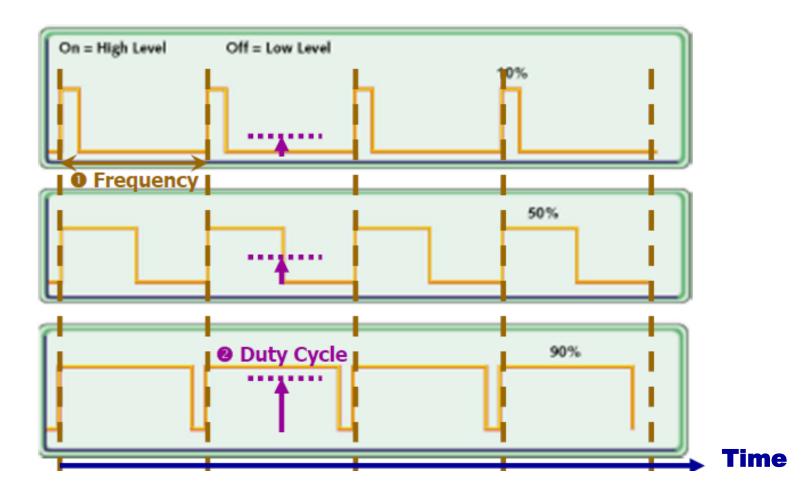

# **PWM** Machines

# Pulse Width Modulation (PWM)

- Pulse width modulation (PWM) is used to control analog circuits with a processor's digital outputs

- PWM is a technique of digitally encoding analog signal levels

- The duty cycle of a square wave is modulated to encode a specific analog signal level

- The PWM signal is still digital because, at any given instant of time, the full DC supply is either fully on or fully off

- The voltage or current source is supplied to the analog load by means of a repeating series of on and off pulses

- Given a sufficient bandwidth, any analog value can be encoded with PWM.

# PWM – Frequency/Duty Cycle

```

Msp430x20x3_ta_16.c

PWM without the processor!

#include <msp430x20x3.h>

void main (void)

WDTCTL = WDTPW + WDTHOLD;

PIDIR |= 0x0C;

PISEL |= 0x0C;

CCR0 = 512-1;

CCTL1 = OUTMOD 7;

CCR1 = 384;

TACTL = TASSEL_2 + MC_1;

```

// Stop WDT

// P1.2 and P1.3 output

// P1.2 and P1.3 TA1/2 options

// PWM Period

// CCR1 reset/set

// CCR1 PWM duty cycle

// SMCLK, up mode

63

5/7/2020 Dr. K. Rasadurai, ECE, KEC

# **Lower Power Saving in MSP430**

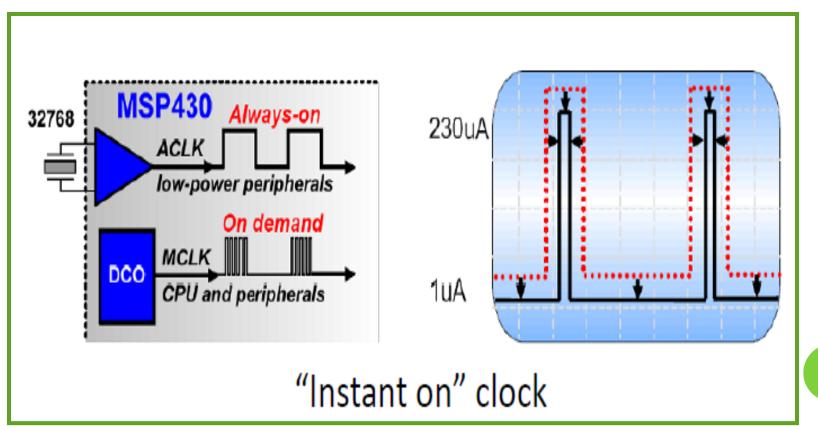

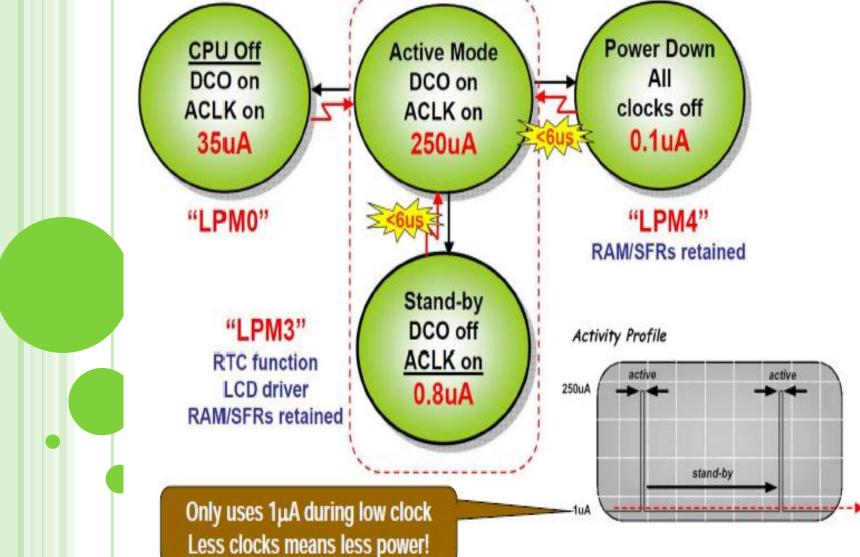

The most important factor for reducing power consumption is using the MSP430 clock system to maximize the time in LPM3

Finally, powering your system with lower voltages means lower power consumption as well.

# LOW POWER MODES

# LOW POWER MODES OF MSP430

• Active mode:

MSP430 starts up in this mode, which must be used when the CPU is required, i.e., to run code

An interrupt automatically switches MSP430 to active

Current can be reduced by running at lowest supply voltage consistent with the frequency of MCLK, e.g. VCC to 1.8V for fDCO = 1MHz

• LPM0:

**CPU and MCLK are disabled**

Used when CPU is not required but some modules require a fast clock from SMCLK and DCO

#### • LPM3:

**Only ACLK remains active**

Standard low-power mode when MSP430 must wake itself at regular intervals and needs a (slow) clock

Also required if MSP430 must maintain a real-time clock

• LPM4:

CPU and all clocks are disabled

MSP430 can be wakened only by an external signal, e.g., RST/NMI, also called *RAM retention mode*

# **Principles of Low-Power Apps** >Maximize the time in LPM3 mode >Use interrupts to wake the processor Switch on peripherals only when needed >Use low-power integrated peripherals **Timer\_A and Timer\_B for PWM** Calculated branches instead of flag polling **Fast table look-ups instead of calculations** >Avoid frequent subroutine and function calls >Longer software routines should use single-cycle >CPU registers

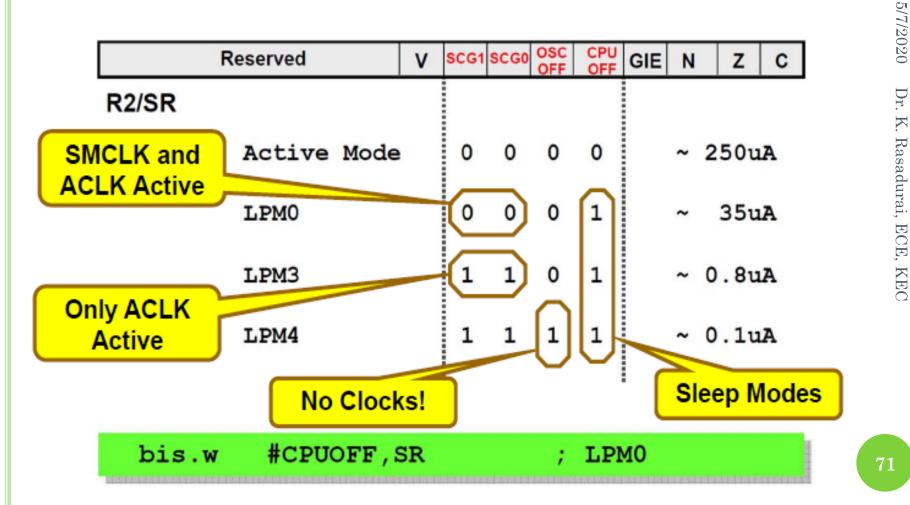

#### **Controlling Low Power Modes**

Through four bits in *Status Register (SR) in CPU*

- SCG0 (System clock generator 0): when set, turns off DCO, If DCOCLK is not used for MCLK or SMCLK

- SCG1 (System clock generator 1) : when set, turns off the SMCLK

- OSCOFF(Oscillator off): when set, turns off LFXT1 crystal oscillator, when LFXT1CLK is not use for MCLK or SMCLK

- CPUOFF (CPU off): when set, turns off the CPU

- All are clear in active mode

# 5/7/2020 Dr. K. Rasadurai, ECE, KEC

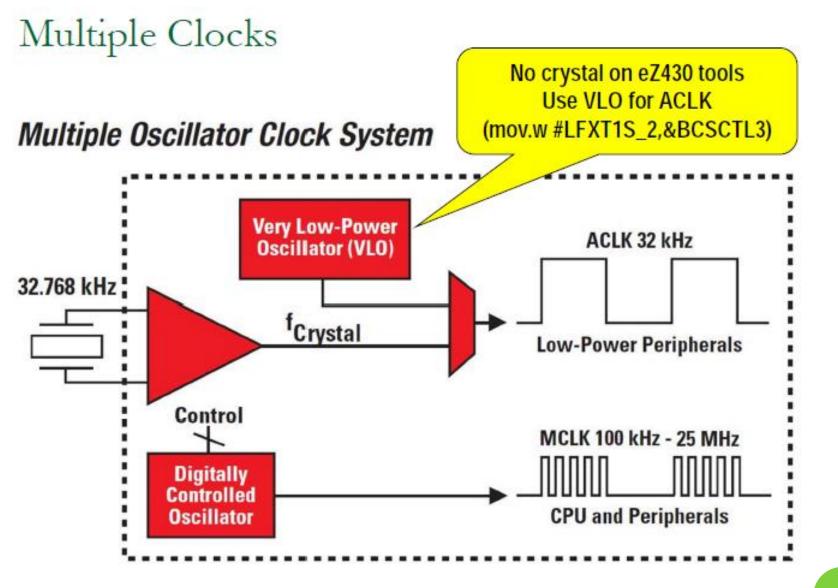

# Processor Clock Speeds

Often, the most important factor for reducing power consumption is slowing the clock down

- Faster clock = Higher performance, more power

- Slower clock = Lower performance, less power

- Using assembly code:

- ; MSP430 Clock Set DCO to 8 MHz: mov.b #CALBC1\_8MHZ,&BCSCTL1 ; Set mov.b #CALDCO\_8MHZ,&DCOCTL ; Set

- ; Set range ; Set DCO step + modulation

# Using C code:

- // MSP430 Clock Set DCO to 8 MHz: BCSCTL1 = CALBC1\_8MHZ; DCOCTL = CALDCO\_8MHZ;

- // Set range 8MHz

// Set DCO step + modulation

# **Controlling Low Power Modes**

#### Status bits and low-power modes

# MSP 430 CLOCK MODES

# STATUS BITS AND LOW-POWER MODES

| SCG1 | SCG0 | OSC<br>OFF | CPU<br>OFF | MODE   | CPU & Clocks Status                                                                                               |

|------|------|------------|------------|--------|-------------------------------------------------------------------------------------------------------------------|

| 0    | 0    | 0          | 0          | ACTIVE | CPU is active, all enabled clocks are active                                                                      |

| 0    | 0    | 0          | 1          | LPM0   | CPU, MCLK are disabled, SMCLK, ACLK are active                                                                    |

| 0    | 1    | 0          | 1          | LPM1   | CPU, MCLK are disabled, DCO and DC<br>generator are disabled if the DCO is not used<br>for SMCLK, ACLK are active |

| 1    | 0    | 0          | 1          | LPM2   | CPU, MCLK, SMCLK, DCO are disabled, DC generator remains enabled, ACLK is active                                  |

| 1    | 1    | 0          | 1          | LPM3   | CPU, MCLK, SMCLK, DCO are disabled, DC generator remains disabled, ACLK is active                                 |

| 1    | 1    | 1          | 1          | LPM4   | CPU and all clocks disabled                                                                                       |

## **ENTERING/EXITING LOW-POWER MODES**

Interrupt wakes MSP430 from low-power modes:

- Enter ISR:

- PC and SR are stored on the stack

- CPUOFF, SCG1, OSCOFF bits are automatically reset entering active mode

- MCLK must be started so CPU can handle interrupt

- Options for returning from ISR:

- Original SR is popped from the stack, restoring the previous operating mode

- SR bits stored on stack can be modified within ISR to return to a different mode when RETI is executed

# Setting Low-Power Modes

- Setting low-power mode puts the microcontroller "to sleep" – so usually, interrupts would need to be enabled as well.

- Enter LPM3 and enable interrupts using assembly code:

- ; enable interrupts / enter low-power mode 3

bis.b #LPM3+GIE,SR ; LPM3 w/interrupts

- Enter LPM3 and enable interrupts using C code:

- // enable interrupts / enter low-power mode 3

\_\_\_\_\_bis\_SR\_register(LPM3\_\_bits + GIE);

# SAMPLE CODE (MSP430G2XX1 \_TA\_01)

```

void main(void) { //Toggle P1.0 every 50000 cycles

WDTCTL = WDTPW + WDTHOLD; // Stop WDT

P1DIR |= 0x01;

// P1.0 output

// CCR0 interrupt enabled

CCTL0 = CCIE;

CCR0 = 50000;

TACTL = TASSEL 2 + MC 2; // SMCLK, contmode

BIS SR(LPMO bits + GIE); // LPMO w/ interrupt

Use _BIC_SR_IRQ(LPM0 bits)

#pragma vector=TIMERA0 VECTOR to exit LPMO

interrupt void Timer A (void) {

// Toggle P1.0

P1OUT ^{=} 0x01;

// Add Offset to CCR0

CCR0 += 50000;

```

# 5/7/2020 Dr. K. Rasadurai, ECE, KEC

#### Flash green LED at 0.5 Hz using interrupt from Timer\_A, driven by ACLK sourced by VLO in LPM3.

•While pushing the button:

- Change from LPM3 to LPM0

- Wake up every 1 sec using interrupt from Timer A driven by SMCLK sourced by

#### VLO.

- On wake up, measure the temperature. If the temperature is higher than 737, flash the red LED at 5 Hz; otherwise flash the green LED at 1 Hz.

### TIMERS

1. Watchdog timer:

Its main function is to protect the system against malfunctions but it can instead be used as an interval timer if this protection is not needed. (*petting*, *feeding*, *or kicking the dog*)

2. Timer\_A: It typically has three channels and is much more versatile than the simpler timers. Timer\_A can handle external inputs and outputs directly to measure frequency, time-stamp inputs, and drive outputs at precisely specified times, either once or periodically.

There are internal connections to other modules so that it can measure the duration of a signal from the comparator, for instance. *It can also generate interrupts*.

3. Timer\_B: Included in larger devices of all families. It is similar to Timer\_A with some extensions that make it more suitable for driving outputs such as pulse-width modulation. Against this, it lacks a feature of sampling inputs in Timer\_A that is useful in communication.

# **TIMERS**

4. *Basic timerf.* **Present in the MSP430x4xx family only.**

It provides the clock for the LCD and acts as an interval timer. Newer devices have the LCD\_A controller, which contains its own clock generator and frees the basic timer from this task.

5. *Real-time clock*: In which the basic timer has been extended to provide a realtime clock in the most recent MSP430x4xx devices.

- The main applications of timers are to:

- generate events of fixed time-period

- allow periodic wakeup from sleep of the device

- count transitional signal edges

- replace delay loops allowing the CPU to sleep between operations, consuming less power

- maintain synchronization clocks

## WATCHDOG TIMER

- To protect the system against failure of the software, such as the program becoming trapped in an <u>unintended</u>, <u>infinite loop</u>. Left to itself,

- **The watchdog counts up and resets the MSP430 when it reaches its limit.**

- □ Keep clearing the counter before the limit is reached to prevent a reset.

- Operation of WDT is controlled by the 16-bit register <u>WDTCTL.</u>

- **D** Password <u>WDTPW = 0x5A</u> in the upper byte.

- □ A reset will occur if a value with an incorrect password is written to WDTCTL.

- **This can be done deliberately if you need to reset the chip from software.**

- Reading WDTCTL returns 0x69 in the upper byte, so reading WDTCTL & writing the value back violates the password and causes a reset.

THE LOWER BYTE OF THE WATCHDOG TIMER CONTROL REGISTER WDTCTL

| 7            | 6             | 5      | 4             | 3             | 2       | 1      | 0      |

|--------------|---------------|--------|---------------|---------------|---------|--------|--------|

| WDT-<br>HOLD | WDT-<br>NMIES | WDTNMI | WDT-<br>TMSEL | WDT-<br>CNTCL | WDTSSEL | WD     | TISx   |

| <br>rw-(0)   | rw-(0)        | rw-(0) | rw-(0)        | r0(w)         | rw-(0)  | rw-(0) | rw-(0) |

- The lower byte of WDTCTL contains the bits that control the operation of the watchdog timer.

- The RST/NMI pin is also configured using this register (which not forget when servicing the watchdog)

- Most bits are reset to 0 after a power-on reset (POR) but are unaffected by a power-up clear (PUC).

- This distinction is important in handling resets caused by the watchdog.

- The exception is the WDTCNTCL bit, labeled r0(w). This means that the bit always reads as 0 but a 1 can be written to stimulate some action, clearing the counter in this case.

## WATCHDOG COUNTER

- The watchdog counter is a 16-bit register <u>WDTCNT</u>, which is not visible to the user.

- It is clocked from either SMCLK or ACLK, according to the WDTSSEL bit.

- The reset output can be selected from bits 6, 9, 13, or 15 of the counter. Thus the period is  $2^6 = 64$ , 512, 8192, or 32,768 times the period of the clock.

- This is controlled by the WDTISx bits in WDTCTL. The intervals are roughly 2, 16, 250, and 1000 ms if the watchdog runs from ACLK at 32 KHz.

- The watchdog is always active after the MSP430 has been reset. By default the clock is SMCLK, which is in turn derived from the DCO at about 1 MHz.

- The default period of the watchdog is the maximum value of 32,768 counts, which is therefore around 32 ms.

- You must clear, stop, or reconfigure the watchdog before this time has elapsed.

#### Program wdtest1.c to demonstrate the watchdog timer.

- selected the clock from ACLK (WDTSSEL = 1) and the longest period (WDTISx = 00), which gives 1s with a 32 KHz crystal for ACLK. (restart)

- LED1 shows the state of button B1 and LED2 shows WDTIFG.

- The watchdog is serviced by rewriting the configuration value in a loop while button B1 is held down.

down. -If the button is left up for more than 1s the watchdog times out, raises the flag WDTIFG, and resets the device with a PUC. This is shown by LED2 lighting.

Dr. K. Rasadurai, ECE, KEC

```

//-----

_____

// Specific device

#include <io430x11x1.h>

Pins for LEDs and button

#define LED1 P2OUT bit.P2OUT 3

#define LED2 P2OUT bit.P2OUT 4

#define B1 P2IN bit.P2IN 1

// Watchdog config: active, ACLK/32768 -> 1s interval; clear counter

#define WDTCONFIG (WDTCNTCL | WDTSSEL)

// Include settings for _RST/NMI pin here as well

//-----

void main (void)

WDTCTL = WDTPW | WDTCONFIG; // Configure and clear watchdog

P2DIR = BIT3 | BIT4;

// Set pins with LEDs to output

P2OUT = BIT3 | BIT4;

// LEDs off (active low)

for (;;) {

// Loop forever

LED2 = ~IFG1 bit.WDTIFG; // LED2 shows state of WDTIFG

// Button up

if (B1 == 1) {

// LED1 off

LED1 = 1;

} else {

// Button down

WDTCTL = WDTPW | WDTCONFIG; // Feed/pet/kick/clear watchdog

LED1 = 0;

// LED1 on

```

## WATCHDOG TIMER...

#### a. Fail - safe Clock Source for Watchdog Timer+

- This includes fail-safe logic to preserve the watchdog's clock.

- Suppose that the watchdog is configured to use ACLK and the program enters low-power mode 4 to wait for an external interrupt,

- i. The old watchdog (WDT) stops during LPM4 and resumes counting when the device is awakened.

- ii. WDT+ does not let the device enter LPM4 because that would disable its clock. Therefore it is not possible to use LPM4 with WDT+ active; the watchdog must first be stopped by setting WDTHOLD.

- iii. Similarly, it is not possible to use LPM3 if WDT+ is active and gets its clock from SMCLK.

- iv. If its clock fails, WDT+ switches from ACLK or SMCLK to MCLK and takes this from the DCO if an external crystal fails.

- The watchdog interval may change dramatically but there must be serious problems elsewhere if this happens.

- Newer devices, including the MSP430F2xx family and recent members <sup>84</sup> of the MSP430x4xx, have the enhanced watchdog timer+ (WDT+).

## WATCHDOG TIMER...

- 2. Watchdog as an Interval Timer

- The watchdog can be used as an interval timer if its protective function is not desired.

- Set the WDTTMSEL bit in WDTCTL for interval timer mode.

- The periods are the same as before and again WDTIFG is set when the timer reaches its limit, but no reset occurs.

- The counter rolls over and restarts from 0.

- An interrupt is requested if the WDTIE bit in the special function register IE1 is set.

- This interrupt is maskable and as usual takes effect only if GIE is also set.

- The watchdog timer has its own interrupt vector, which is fairly high in priority but not at the top.

- It is not the same as the reset vector, which is taken if the counter times out in watchdog mode.

- The WDTIFG flag is automatically cleared when the interrupt is serviced. It can be polled if interrupts are not used.

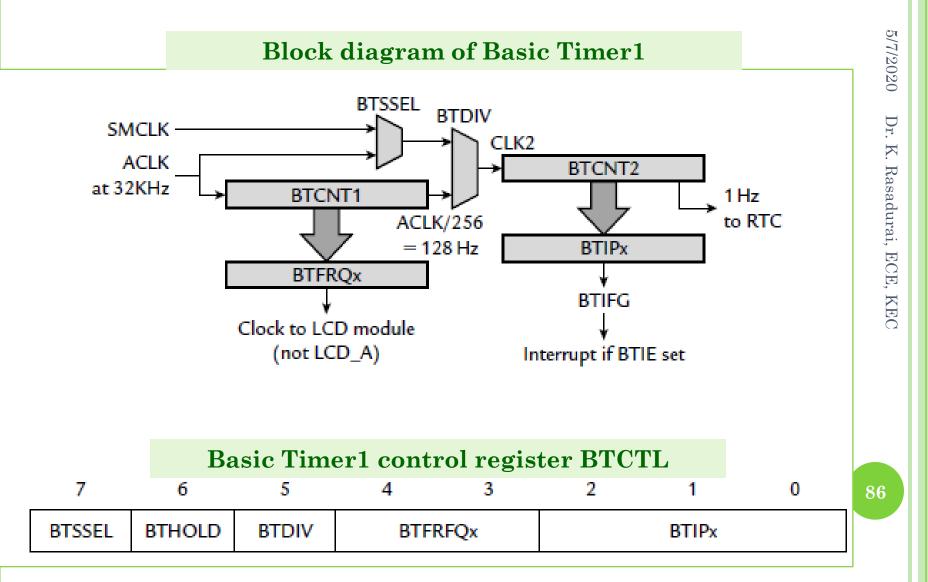

## **BASIC TIMER1**

It provides the clock for the LCD module and generates periodic interrupts. (a real-time clock driven by a signal at 1Hz)

# **REAL-TIME CLOCK**

- It counts seconds, minutes, hours, days, months, and years.

- Alternatively it can be used as a straight forward

- It is configured in calendar mode by setting RTCMODEx=11 in the control register RTCCTL.

| 7      | 6       | 5    | 4        | 3 | 2    | 1     | 0     |

|--------|---------|------|----------|---|------|-------|-------|

| RTCBCD | RTCHOLD | RTCM | RTCMODEx |   | TEVx | RTCIE | RTCFG |

The Real-Time Clock control register RTCCTL.

a power-on reset, unlike BTCTL, and the RTCHOLD bit is set so that the clock does not run by default.

The current time and date are held in a set of registers that contain the following bytes:

- Second (RTCSEC).

- Minute (RTCMIN).

- Hour (RTCHOUR), which runs from 0–23 (24-hour format).

- Day of week (RTCDOW), which runs from 0–6.

- Day of month (RTCDAY).

- Month (RTCMON).

- Year (RTCYEARL), assuming BCD format.

- Century (RTCYEARH), assuming BCD format.

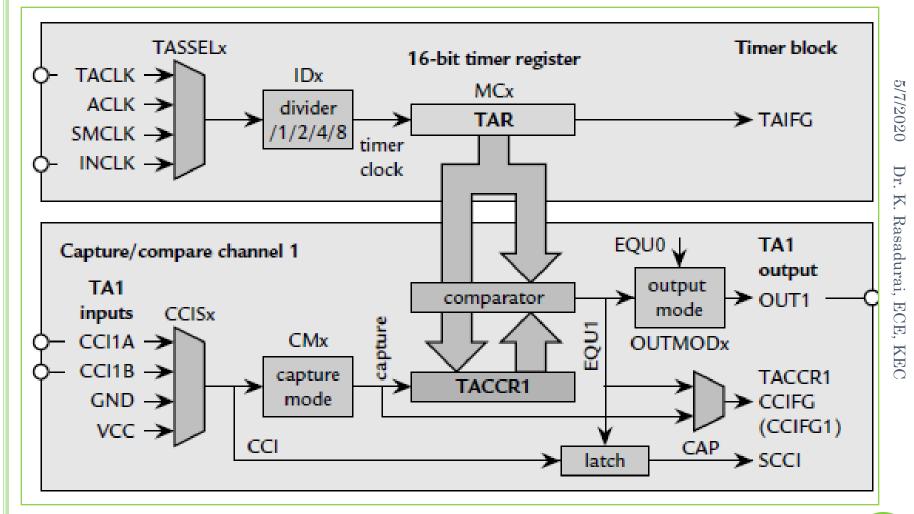

## TIMER\_A

• Two main parts to the hardware:

- a. Timer block: The core, based on the 16-bit register TAR. There is a choice of sources for the clock, whose frequency can be divided down (prescaled). The timer block has no output but a flag TAIFG is raised when the counter returns to 0.

- b. Capture/compare channels: In which most events occur, each of which is based on a register TACCRn. They all work in the same way with the important exception of TACCR0. Each channel can

- Capture

- Compare

- Request an interrupt

- Sample

#### BLOCK DIAGRAM OF TIMER\_A :

THE TIMER BLOCK AND CAPTURE / COMPARE CHANNEL 1

The circles show external signals that may be brought out to pins of the device.

#### TIMER BLOCK

a 16-bit timer register TAR, which is central to the operation of the timer.

It can be chosen from four sources by using the TASSELx bits:

| • SMCLK  |

|----------|

| •ACLK    |

| •TACLK   |

| • INCLK. |

| Inpu   | ıt clock  | Tim                      | er clock          | Range of timer    |        |  |

|--------|-----------|--------------------------|-------------------|-------------------|--------|--|

| Source | Frequency | uency Divider Resolution |                   | Frequency         | Period |  |

| SMCLK  | 16 MHz    | 1                        | $\frac{1}{16}$ µs | 240 Hz            | 4ms    |  |

| SMCLK  | 1 MHz     | 1                        | 1 μs              | 15 Hz             | 66 ms  |  |

| SMCLK  | 1 MHz     | 8                        | 8 µ.s             | 2 Hz              | 0.5s   |  |

| ACLK   | 32 KHz    | 1                        | 31 µs             | $\frac{1}{2}$ Hz  | 2 s    |  |

| ACLK   | 32 KHz    | 8                        | 240 µs            | $\frac{1}{16}$ Hz | 16s    |  |

90

# TxCTL Control Register

| 15  | 14   | 13                      | 12                  | 11      | 10      | 9       | 8      | 7      | 6                                                                                                               | 5               | 4           | 3 | 2     | 1    | 0     |

|-----|------|-------------------------|---------------------|---------|---------|---------|--------|--------|-----------------------------------------------------------------------------------------------------------------|-----------------|-------------|---|-------|------|-------|

|     | (Us  | (Used by Timer_B) TxSSE |                     |         |         |         | SELx   | 10     | Dx                                                                                                              | M               | Cx          | - | TXCLR | TxIE | TxIFG |

| Bit |      | Description             |                     |         |         |         |        |        |                                                                                                                 |                 |             |   |       |      |       |

| 9-8 | TxS  | SELX                    | Tin                 | ner_x ( | clock s | ource   | :      | 0<br>1 | $\begin{array}{l} 0 \Rightarrow T \\ 1 \Rightarrow A \\ 0 \Rightarrow S \\ 1 \Rightarrow I N \end{array}$       | CLK<br>MCLK     |             |   |       |      |       |

| 7-6 | IDx  |                         | Clock signal divide |         |         |         |        | 0<br>1 | $\begin{array}{c} 0 \Rightarrow / 1 \\ 1 \Rightarrow / 2 \\ 0 \Rightarrow / 4 \\ 1 \Rightarrow / 8 \end{array}$ | 2<br>4          |             |   |       |      |       |

| 5-4 | MC   | MCx Clock timer oper    |                     |         |         | erating | mode:  | 0<br>1 | $\begin{array}{l} 0 \Rightarrow St \\ 1 \Rightarrow U \\ 0 \Rightarrow C \\ 1 \Rightarrow U \end{array}$        | p mod<br>ontinu | e<br>ous mo |   |       |      |       |

| 2   | TxC  | LR                      | Tin                 | ner_x ( | clear w | hen T   | xCLR = | 1      |                                                                                                                 |                 |             |   |       |      |       |

| 1   | TXIE |                         | Tin                 | ner_x i | interru | pt ena  | ble wh | en Txl | E = 1                                                                                                           |                 |             |   |       |      |       |

| 0   | TXIF | G                       | Tin                 | ner_x i | interru | pt pen  | ding w | hen T  | xIFG =                                                                                                          | 1               |             |   |       |      |       |

5/7/2020 Dr. K. Rasadurai, ECE, KEC

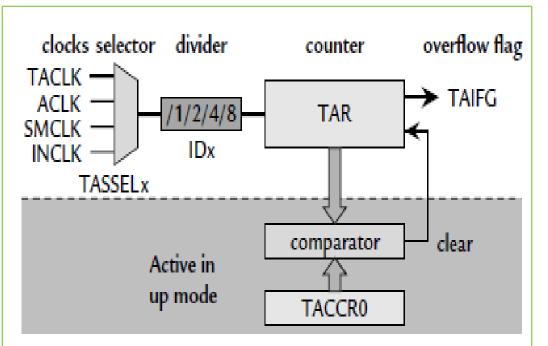

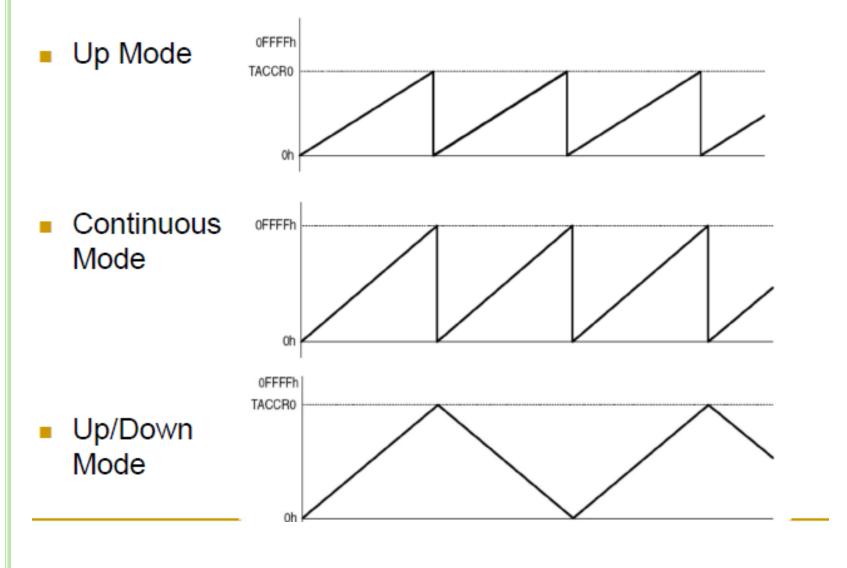

# 4 Modes of Operation

- Timer reset by writing a 0 to TxR

- Clock timer operating modes:

| MCx | Mode       | Description                                                                                              |

|-----|------------|----------------------------------------------------------------------------------------------------------|

| 0 0 | Stop       | The timer is halted.                                                                                     |

| 0 1 | Up         | The timer repeatedly counts from 0x0000 to<br>the value in the TxCCR0 register.                          |

| 10  | Continuous | The timer repeatedly counts from 0x0000 to<br>0xFFFF.                                                    |

| 11  | Up/down    | The timer repeatedly counts from 0x0000 to<br>the value in the TxCCR0 register and<br>back down to zero. |

# Timer Modes

5/7/2020 Dr. K. Rasadurai, ECE, KEC

| 15      | 14         |       | 13                | 12                                        | 11                              | 10                 | 9                 | 8          |

|---------|------------|-------|-------------------|-------------------------------------------|---------------------------------|--------------------|-------------------|------------|

|         |            |       | Unu               | ised                                      | 100.000                         |                    | TAS               | SELx       |

| rw-(0)  | rw-(0)     |       | rw-(0)            | rw-(0)                                    | rw-(0)                          | rw-(0)             | rw-(0)            | rw-(0)     |

| 7       | 6          |       | 5                 | 4                                         | 3                               | 2                  | 1                 | 0          |

|         | IDx        |       | M                 | Cx                                        | Unused                          | TACLR              | TAIE              | TAIFG      |

| rw-(0)  | rw-(0)     |       | rw-(0)            | rw-(0)                                    | rw-(0)                          | rw-(0)             | rw-(0)            | rw-(0)     |

| Unused  | Bits 15-10 | Unuse | ed                |                                           |                                 |                    |                   |            |

| TASSELX | Bits 9-8   | Timer | A clock source    | e select                                  |                                 |                    |                   |            |

|         |            | 00    | TACLK             |                                           |                                 |                    |                   |            |

|         |            | 01    | ACLK              |                                           |                                 |                    |                   |            |

|         |            | 10    | SMCLK             |                                           |                                 |                    |                   |            |

|         |            | 11    |                   | LK is device-spec<br>ific data sheet)     | ific and is often as            | signed to the inve | ted TBCLK) (see   | the        |

| Dx      | Bits 7-6   | Input | divider. These I  | bits select the divi                      | ider for the input cl           | lock.              |                   |            |

|         |            | 00    | /1                |                                           |                                 |                    |                   |            |

|         |            | 01    | 12                |                                           |                                 |                    |                   |            |

|         |            | 10    | 14                |                                           |                                 |                    |                   |            |

|         |            | 11    | /8                |                                           |                                 |                    |                   |            |

| MCx     | Bits 5-4   | Mode  | control. Setting  | MCx = 00h when                            | n Timer_A is not in             | use conserves po   | ower.             |            |

|         |            | 00    | Stop mode:        | the timer is halted                       | L                               |                    |                   |            |

|         |            | 01    | Up mode: th       | e timer counts up                         | to TACCRD.                      |                    |                   |            |

|         |            | 10    | Continuous        | mode: the timer o                         | ounts up to OFFFF               | h.                 |                   |            |

|         |            | 11    | Up/down mo        | de: the timer cou                         | nts up to TACCR0                | then down to 000   | Oh.               |            |

| Unused  | Bit 3      | Unuse | ed                |                                           |                                 |                    |                   |            |

| TACLR   | Bit 2      |       |                   | ig this bit resets T<br>nd is always read | AR, the clock divid<br>as zero. | ter, and the count | direction. The TA | CLR bit is |

| TAIE    | Bit 1      | Timer | _A interrupt en   | able. This bit enal                       | bles the TAIFG inte             | errupt request.    |                   |            |

|         |            | 0     | Interrupt disa    | abled                                     |                                 |                    |                   |            |

|         |            | 1     | Interrupt end     | abled                                     |                                 |                    |                   |            |

| TAIFG   | Bit 0      | Timer | _A interrupt flag | 9                                         |                                 |                    |                   |            |

|         |            | 0     | No interrupt      | pending                                   |                                 |                    |                   |            |

|         |            |       |                   |                                           |                                 |                    |                   |            |

#### 12.3.2 TAR, Timer\_A Register

| 15     | 14            | 13                  | 12                  | 11                | 10     | 9      | 8      |

|--------|---------------|---------------------|---------------------|-------------------|--------|--------|--------|

|        |               |                     | TA                  | Rx                |        |        |        |

| rw-(0) | rw-(0)        | rw-(0)              | rw-(0)              | rw-(0)            | rw-(0) | rw-(0) | rw-(0) |

| 7      | 6             | 5                   | 4                   | 3                 | 2      | 1      | 0      |

|        |               |                     | TA                  | Rx                |        |        |        |

| rw-(0) | rw-(0)        | rw-(0)              | rw-(0)              | rw-(0)            | rw-(0) | rw-(0) | rw-(0) |

| TARx   | Bits 15-0 Tir | mer_A register. The | e TAR register is t | he count of Timer | _A.    |        |        |

#### 12.3.3 TACCRx, Timer\_A Capture/Compare Register x

| 15     | 14        | 13                                | 12                | 11                 | 10                 | 9                  | 8           |

|--------|-----------|-----------------------------------|-------------------|--------------------|--------------------|--------------------|-------------|

|        |           |                                   | TAC               | CRx                |                    |                    |             |

| rw-(0) | rw-(0)    | rw-(0)                            | rw-(0)            | rw-(0)             | rw-(0)             | rw-(0)             | rw-(0)      |

| 7      | 6         | 5                                 | 4                 | 3                  | 2                  | 1                  | 0           |

|        |           |                                   | TAC               | CRx                |                    |                    |             |

| rw-(0) | rw-(0)    | rw-(0)                            | rw-(0)            | rw-(0)             | rw-(0)             | rw-(0)             | rw-(0)      |

| TACCRX | Bits 15-0 | Timer_A capture/con               | pare register.    |                    |                    |                    |             |

|        |           | Compare mode: TAC<br>TAR.         | CRx holds the da  | ta for the compari | son to the timer v | alue in the Timer_ | A Register, |

|        |           | Capture mode: The T<br>performed. | Timer_A Register, | TAR, is copied in  | to the TACCRx re   | gister when a cap  | ture is     |

| OUTMODx | Mode         | Description                                                                                                                                                                     |

|---------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000     | Output       | The output signal OUTx is defined by the OUTx bit. The OUTx signal updates immediately<br>when OUTx is updated.                                                                 |

| 001     | Set          | The output is set when the timer <i>counts</i> to the TACCRx value. It remains set until a reset of the timer, or until another output mode is selected and affects the output. |

| 010     | Toggle/Reset | The output is toggled when the timer counts to the TACCRx value. It is reset when the timer<br>counts to the TACCR0 value.                                                      |

| 011     | Set/Reset    | The output is set when the timer counts to the TACCRx value. It is reset when the timer<br>counts to the TACCR0 value.                                                          |

| 100     | Toggle       | The output is toggled when the timer counts to the TACCRx value. The output period is double the timer period.                                                                  |

| 101     | Reset        | The output is reset when the timer counts to the TACCRx value. It remains reset until another<br>output mode is selected and affects the output.                                |

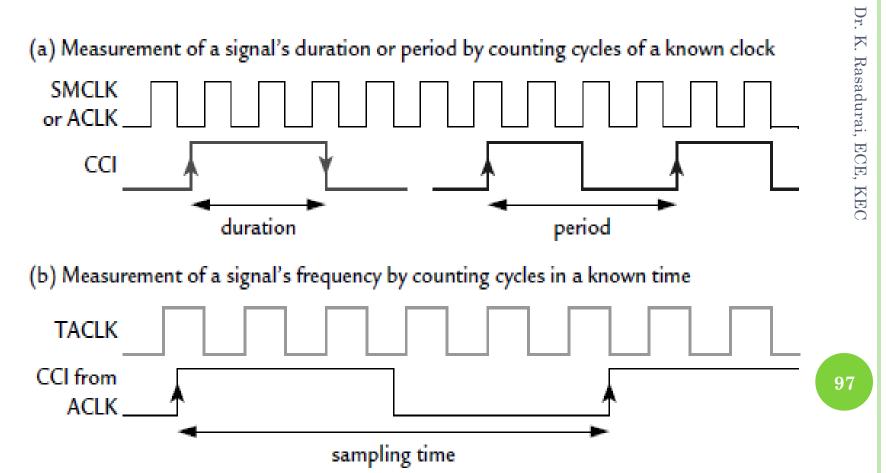

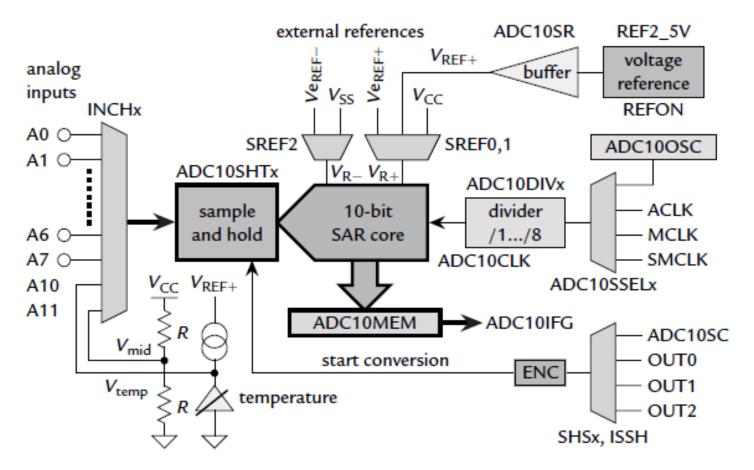

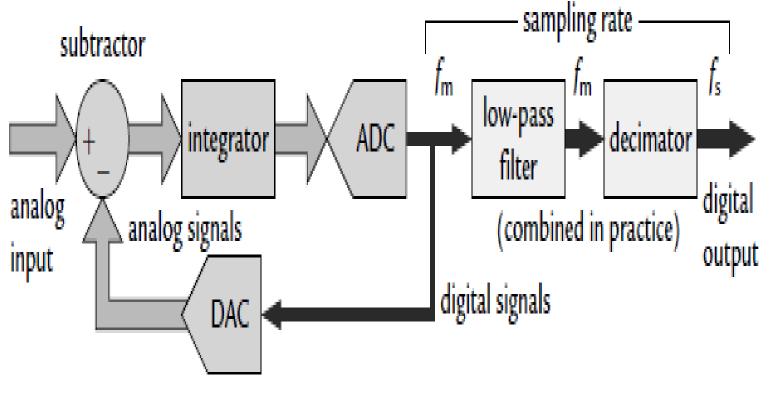

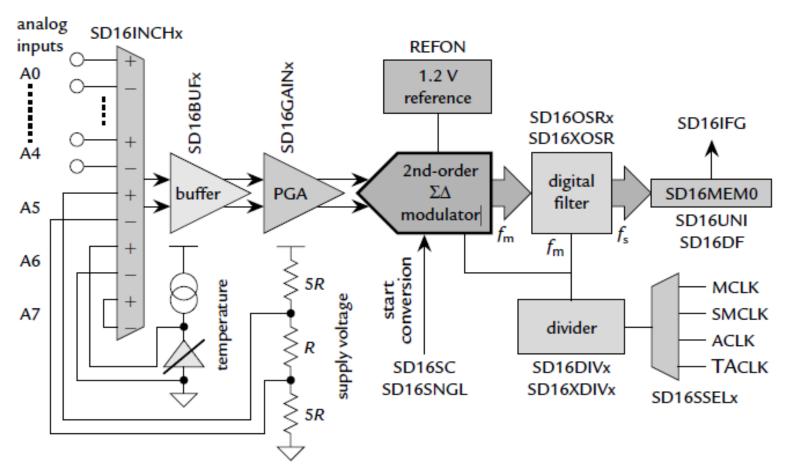

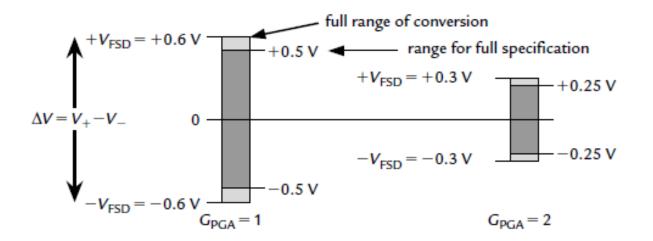

| 110     | Toggle/Set   | The output is toggled when the timer counts to the TACCRx value. It is set when the timer<br>counts to the TACCR0 value.                                                        |